Flash-ADC mit 7-Segment-Anzeige

Funktionsweise eines Analog-Digital-Wandlers im Parallelverfahren (Flash-ADC)

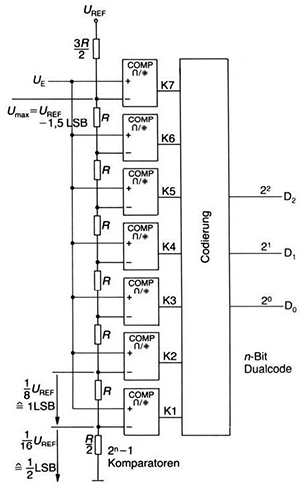

Allgemeiner Aufbau

Ein Analog-Digital-Wandler im Parallelverfahren besteht aus zwei Baugruppen. Der Komparator- und der Encoderstufe (Prioritätsencoder). Die Komparatorstufe besteht aus mehreren einzelnen Komparatoren. Die genau Anzahl hängt von der Auflösung (Bitanzahl) des gewünschten ADCs ab. Für jede darstellbare Stufe wird ein eigener Komparator benötigt. Berechnen lässt sich die Anzahl der benötigten Komparatoren über die folgende Formel: Anzahl = 2^n -1 wobei n der Anzahl der darzustellenden Bits entspricht.

Für den hier entworfenen 3Bit-ADC bedeutet dies, wir benötigen Anzahl = 2³ – 1 = 7 Komparatoren. Bei einem in der Praxis eher üblichen 8Bit-ADC würden bereits 255 Komparatoren benötigt werden.

Aufbau und Funktionsweise der Komparatorstufe

An den invertierenden Eingängen (-) der Komparatoren liegt eine feste, sehr stabile Referenzspannung an. Diese wird durch eine Spannungsteilerkette, mit gleich großen Widerständen in n Stufen eingeteilt. Es gibt zwei Abweichungen von diesen Werten. Um einen kleineren Quantisierungsfehler zu erhalten, ist der erste Widerstand der Kette 3R/2 groß. Damit liegt die erste Schaltschwelle bei 1/16*URef. Die folgenden Abstufungen sind immer 1/8*URef. Bei dieser Kombination ist auch der letzte Widerstand in der Kette verändert; der Wert liegt bei R/2.

Die Schaltschwellen können mit Hilfe einer Formel bestimmt werden. Für einen 3Bit-ADC gilt: USchalt = URef * (2n +1 /16). n ist dabei der Index für die Anzahl der vorhandenen Widerstände, der unterste hat den Index 0. Die höchste Teilspannung in dieser Widerstandskette stellt das MSB (most significant bit = höchstwertigste Bit) und die kleinste Spannung das LSB (least significant bit) dar. Die höchste Spannung die verarbeitet werden kann, berechnet sich mit Hilfe von URef und ULSB: UA = URef – ULSB. Durch diese Berechnung ergibt sich ein ein minimaler Fehler, der Quantisierungsfehler. Um diesen gering zu halten, werden ADCs mit einer höheren Auflösung (z.B. 10Bit) verwendet. Durch die größer Anzahl der darstellbaren Stufen, verringert sich der Fahler der bei der Umwandlung von Analog zu Digital entsteht.

An den nichtinvertierenden Eingängen (+) der Komparatoren liegt die zu wandelnde Spannung an. Die Spannungen beider Eingänge werden miteinander verglichen; ist die Spannung am invertierenden Eingang höher als die am nichtinvertierenden Eingang, so bekommen wir ein „low“-Signal ( 0V oder -UB) am Ausgang dieses Komparators. Ist die Spannung am invertierenden Eingang niedriger als am nichtinvertierenden Eingang, so bekommen wir am Ausgang des Komparators ein „high“-Signal (+UB). Um ein Schwingen der Schaltung um den Nullpunkt zu vermeiden, werden die Komparatoren um eine Schalthysterese (auch Schmitt-Trigger genannt) ergänzt. (Nicht in der Abbildung enthalten)

Aufbau und Funktionsweise der Codierstufe

Die Kodierstufe besteht im Wesentlichen aus verschiedenen Logik-Gattern (not, and- und or-Gatter). Diese „übersetzt“ die „high“- und „low“- Signale der vorgeschalteten Komparatorstufe, sogenannten Thermometercode, in eine Binärzahl. Die Codierstufe auf dem linken Bild, weist den Ausgangszuständen der Komparatoren eine Größe Zk zu. Zk ist proportional zur Wertigkeit des „höchsten“ Komparators, der ein „high“-Signal liefert. Nimmt die umzuwandelnde Größe Werte von 0V bis URef an, so erhält die Binärgröße die Werte 000 -111 (bei unserem 3Bit ADC).

Geschwindigkeit des Analog-Digital-Wandlers im Parallelverfahren

Die Geschwindigkeit des Analog-Digital-Wandlers wird durch zwei Punkte bestimmt:

- Geschwindigkeit der Komparatoren

- Geschwindigkeit der Codierstufe (propagation delay)

Die Geschwindigkeit der Komparatoren ist sehr schnell, durch die parallele Ausführung der Komparatorstufen ist dies sehr schnell. Die Geschwindigkeit der Codierstufe liegt bei heutigen Wandlern mit einer Auflösung von 4-8Bit bei ca. 10ns.

Schaltungsaufwand

Der Schaltungsaufwand einen Analog-Digital-Wandlers im Parallelverfahren ist sehr hoch. Da für jede einzelne Stufe ein eigener Komparator benötigt wird, ist bei Wandlern mit einer hohen Auflösung die Anzahl der Komparatoren sehr groß. Für einen (mittelmäßigen) ADC mit 8Bit werden 255 Komparatoren benötigt. Durch diese vielen Komparatoren ist der Energiebedarf eines solchen Wandlers sehr groß, auch die Herstellung ist aufwendig und teuer. Dennoch eignet er sich aus schaltungstechnischer Sicht in ein einzelnes IC zu integrieren.

- Alle Widerstände (bis auf den Ersten und Letzten) sind gleich groß

- Die absolute Größe der Widerstände ist unerheblich, Wichtig sind minimale Toleranzen

- Typische Widerstandswerte sind 1kOhm bis 10 kOhm

Quantisierungsfehler

Bei der Umwandlung von analogen Signalen zu Digitalen ergibt sich ein kleiner Fehler, der Quantisierungsfehler. Dieser entsteht durch die „Treppchenbildung“ bei der Wandlung. Im Gegensatz zu einer analogen Spannung, die unendlich viele Zwischenwerte aufweist, hat eine digitale Spannung eine klar definierte Anzahl an Zwischenwerten. Der Verlust von Spannungswerten einer analogen Spannung aufgrund der Digitalisierung nennt sich Quantisierungsfehler. Der genaue Informations- bzw Wertverlust hängt von der Auflösung des ADCs ab. Die Berechnung der Anzahl (Stufen) der Zwischenwerte erfolgt mit der Full-Scale-Spannung (UFS) und der Auflösung n: UE = UFS / 2^n. Annahme hierbei ist, dass UFS = URef. Dies ist natürlich nur bei einem idealen Wandler der Fall, bei einem Realen ist UFS immer minimal niedriger als URef. Es gilt: UFS = URef / 2^n = URef – LSB.

Die einzige Lösung um den Quantisierungsfehler sehr gering zu halten, ist einen Analog-Digital-Wandler mit einer hohen Auflösung zu wählen. Ab einer Auflösung von 10Bit wird der auftretende Quantisierungsfehler für die meisten Anwendungen irrelevant; er beträgt bei dieser Auflösung nur noch 1/1024 * URef.

Weiterführende Kapitel zu dem Berufsschulprojekt

Funktionsbeschreibung

Blockschaltbild & Schaltpläne

Platinenlayout & Gehäusezeichnungen

Kostenaufstellung

Datenblätter

Bildergallery